Microsoft ends support for Internet Explorer on June 16, 2022.

We recommend using one of the browsers listed below.

- Microsoft Edge(Latest version)

- Mozilla Firefox(Latest version)

- Google Chrome(Latest version)

- Apple Safari(Latest version)

Please contact your browser provider for download and installation instructions.

March 4, 2025

The University of Tokyo

NTT Corporation

RIKEN

Kyushu University

Japan Science and Technology Agency (JST)

New Quantum Computer Architecture with Separate Memory and Processor

Portable, memory-efficient design paves the way to practical quantum computation

News Highlights:

- Redefining the roles of memory and processors under the constraint of "no-cloning theorem", which prohibits the copy of quantum data, we propose a new architecture of fault-tolerant quantum computers that excels in versatility and portability.

- In practical quantum computation, we demonstrate that, compared to conventional quantum computers, our approach can reduce the required hardware resources by approximately 40% while suppressing the overhead of computation time.

- This achievement is expected to contribute to the advancement of quantum computer architecture research and the early realization of fault-tolerant quantum computers.

Research Positioning

Research Positioning

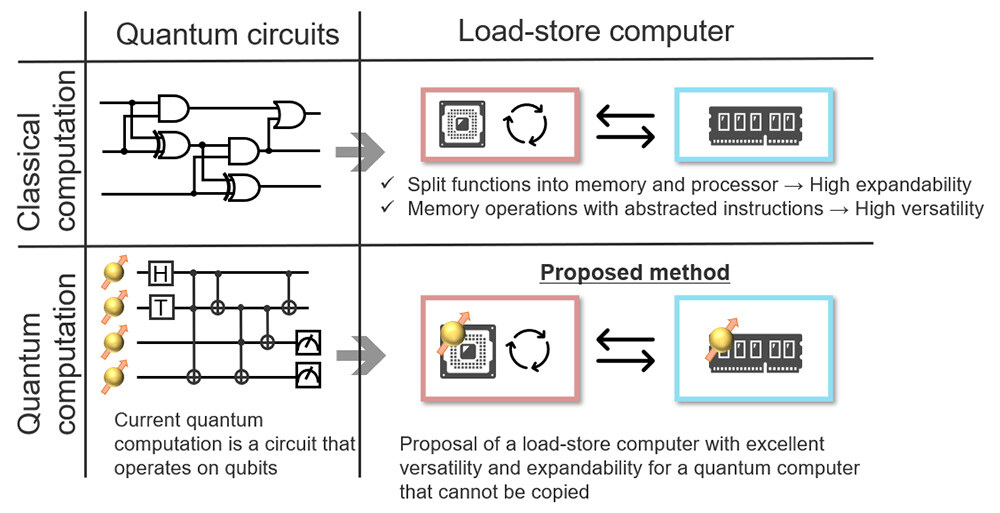

In this study, a load-store-type quantum computing architecture was proposed.

TOKYO - March 4, 2025 - A research group has proposed a new fault-tolerant quantum computing1 architecture2 based on the concept of a load-store architecture, which is the fundamental design of a conventional computer. This approach separates memory and processor, making the architecture highly portable and efficient. The team includes:

- Takumi Kobori, Graduate Student, Graduate School of Science, The University of Tokyo (NTT Corporation intern at the time of the research)

- Synge Todo, Professor, Graduate School of Science, The University of Tokyo

- Yasunari Suzuki, Associate Distinguished Researcher, NTT Corporation

- Yuuki Tokunaga, Distinguished Researcher, NTT Corporation

- Yosuke Ueno, Special Postdoctoral Researcher, RIKEN Center for Quantum Computing

- Teruo Tanimoto, Associate Professor, Faculty of Information Science and Electrical Engineering, Kyushu University

This technology enables efficient utilization of quantum hardware and accelerates the realization of highly portable programs. It represents a major step forward in practical quantum computation.

These findings will be presented at the 31st IEEE International Symposium on High-Performance Computer Architecture (HPCA2025) held from March 1, 2025.

Research Background

Conventional quantum computers are built based on a representation called quantum circuits. This approach assumes that all quantum data is stored in computable registers (memory device), and programs are expressed and executed in a circuit-like form. While this approach is simple and intuitive, it presents a challenge for scaling up. The size of memory devices must be increase while maintaining the ability to perform arbitrary basic operations no matter where the data is stored on the device. Additionally, in this approach, programs are optimized specifically for the details of the devices and error correction methods, making it difficult to port executable files to computers even with slightly different configurations.

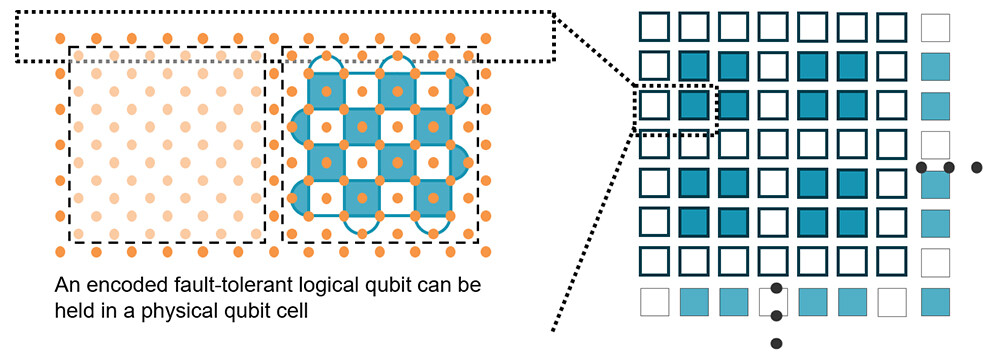

For example, in the mainstream method for fault-tolerant quantum computation using two-dimensionally aligned qubits, a square cell of qubits is used as a code block (blue cell) for encoding logical qubits with quantum error-correcting codes3 called surface codes, as shown in Figure 1. To allow all code blocks to perform arbitrary operations based on quantum circuits, an additional code block (white cell) must be placed next to each cell storing quantum data (blue cell) for assisting calculations. Since these auxiliary cells cannot be used to store data, the fraction of quantum devices that are actually used for data storage has typically been limited between 44% to 67%. This low effective memory utilization has been a major obstacle in developing quantum computers, as scaling these devices is technically challenging.

Figure 1 Conceptual Diagram of Fault-Tolerance Quantum Computation based on Surface Code and Example of Conventional Mapping

Figure 1 Conceptual Diagram of Fault-Tolerance Quantum Computation based on Surface Code and Example of Conventional Mapping

Note. Left: Orange dots represent physical qubits, and each cell is typically composed of hundreds of qubits. The figure shows an example of an implementation using surface codes, and white and blue semicircles and rectangles represent error-check patterns.

Right: The blue cells represent data cells that store logical qubits, and the white cells are auxiliary cells allocated for the operations. Memory efficiency is measured by the ratio of the blue cells to the total number of cells. In the illustrated mapping, the memory efficiency is 44%.

Point of the technology

This research group proposed a load-store-based quantum computer architecture to address the challenges of current quantum computers, such as low memory utilization and limited portability. The load-store architecture is a standard architecture used in modern computers in which a computer is divided into a memory and a processor to perform calculations while exchanging data. Two abstracted instructions, "load" and "store," are used for transferring data between the memory and processor. By describing programs with these instructions, programs can be built in a portable way that does not depend on specific processor or memory device structures. Additionally, the memory is only required to store data, allowing for high memory utilization.

In this joint research, the University of Tokyo and NTT proposed a framework for introducing a load-store architecture and evaluated its performance numerically, while Kyushu University and RIKEN designed a load-store-type function and instruction set and refined the evaluation method as a computer system.

Outline of the study

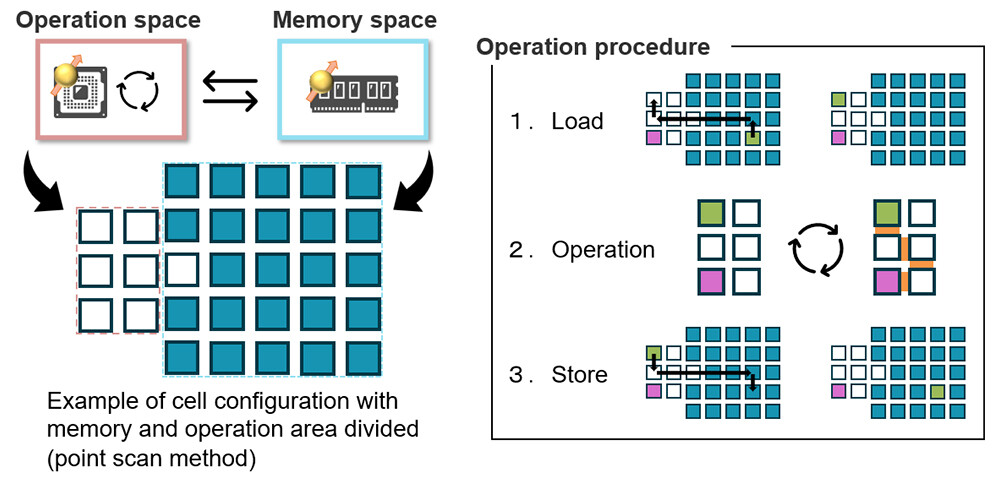

In this research, the team proposed a new quantum computer architecture that utilizes the design concept of the load-store architecture to significantly reduce the quantum hardware required for practical quantum computing while being highly versatile and portable. The concept of a load-store-type computer is well known in conventional computer design. This study demonstrates that an effective load-store-type quantum computer can be constructed by applying this concept to the design of a quantum computer, according to the characteristics and constraints of quantum computers, as shown in Figure 2.

In the proposed load-store-type quantum computation architecture, computation is performed by combining a large memory space and a small computing space that can perform arbitrary basic operations. The data movement between the memory and computing spaces are expressed in an abstracted instruction of load and store, resulting in high portability. This ensures that the architecture can be used effectively, even if the error-correcting codes or hardware designs change. Because data movement in quantum computation has fundamental properties unique to quantum information, such as the no-cloning theorem4, and technical limitations specific to the quantum devices and error correction methods, it was not clear whether such a design could be efficiently implemented. By proposing new quantum memory methods, this study shows that 100% memory efficiency can be achieved asymptotically, and approximately 90% efficiency can be achieved in practical cases.

Figure 2 Overview of the Proposed Method

Figure 2 Overview of the Proposed Method

Note. Left: An example of cell arrangement based on the quantum memory system proposed in this research. Compared with the conventional design shown in Figure 1, the proportion of white cells (auxiliary cells allocated for calculation) is low and the proportion of blue cells (cells holding data) is high, resulting in high memory efficiency. The white cell space on the left represents the computing space, and the space occupied by the blue cell on the right corresponds to the memory space.

Right: The calculation flow proposed in this achievement. This method abstracts data movement and operations, enabling execution regardless of changes in error-correcting codes or hardware.

- Load: A target cell (green cell) held in the right memory space is transferred to the computing space for a processing with a predefined logical operation.

- Operation: A cell in a computing space is operated using an auxiliary cell (white cell) and another preloaded cell (purple cell).

- Store: The processed cell is returned to memory.

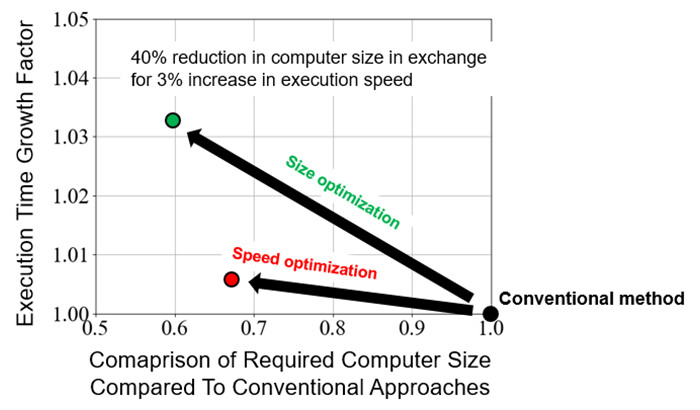

Using load-store computations is often associated with an increase of computation time due to the limited memory bandwidth5 between memory and computing spaces. Conventional computers solve these problems by using a cache structure that takes advantage of the locality of program memory access6 and a mechanism that conceal communication delays with calculation in the computing space. In this research, we translated a typical quantum program into a form executable by a quantum computer and analyzed its memory access patterns. For the first time, it was demonstrated that locality in memory access exists in quantum computers, like conventional computers. Based on these findings, we proposed a cache-like technique to enhance the effective memory communication bandwidth and developed a mechanism to conceal the access delay by overlapping the communication time with other calculations. This approach successfully reduced the computation time increase to approximately 3% compared to a computer that can perform calculations in the entire space of the computer (Figure 3). As a result, the load-store-based quantum computation is an excellent design that can simultaneously achieve both high memory efficiency and portability with only a minimal increase in computation time.

Figure 3 Performance Improvement by the Proposed Method

Figure 3 Performance Improvement by the Proposed Method

Note. Figure shows the performance requirements of a quantum computer when optimized in two settings.

Red dots: Results of speed optimization. The computer's size was reduced by 30%, while the speed increase was limited to 1% or less.

Green dots: Results of size optimization. The computational size was reduced by approximately 40%, with a 3% increase in speed.

Outlook

This research achievement is expected to enable highly efficient utilization of quantum hardware, significantly accelerating the practical application of quantum computation. Additionally, the high program portability of this proposal plays a role in ensuring the compatibility between hardware advancement and error correction methods at the lower layer and the development of technology at the higher layer, such as programming languages and compilation optimization (minimizing program execution time, memory usage, and power consumption, etc.). This facilitates the promotion of parallel advanced research in large-scale quantum computer development.

This research is significant as it demonstrates that the concepts of load, store, and cache, fundamental in conventional computer architecture, are also effective in the quantum computer field. It is anticipated that this work will catalyze active research and development across both computer architecture and quantum computers, ultimately establishing the foundational design of practical quantum computation.

Paper announcement

Conference name: The 31st IEEE International Symposium on High-Performance Computer Architecture (HPCA 2025), on March 1, under the following title and authors.

Title: "LSQCA: Resource-Efficient Load/Store Architecture for Limited-Scale Fault-Tolerant Quantum Computing"

Authors: Takumi Kobori, Yasunari Suzuki, Yosuke Ueno, Teruo Tanimoto, Synge Todo, Yuuki Tokunaga

Support for this research

The study was supported by the Japan Science and Technology Agency (JST) Moonshot Research & Development Program Moonshot Goal 6 "Realization of a fault-tolerant universal quantum computer that will revolutionize economy, industry, and security by 2050" (Program Director: Masahiro Kitagawa, Director, Center for Quantum Information and Quantum Biology, Osaka University) Research and Development Project, "Research and Development of Theory and Software for Fault-tolerant Quantum Computers" (Project Manager): Masato Koashi, Professor, Graduate School of Engineering, The University of Tokyo) (JPMJMS2061), "Development of Integration Technologies for Superconducting Quantum Circuits" (Project Manager): Tsuyoshi Yamamoto, Research Fellow, Secure System Platform Research Laboratories, NEC Corporation) (JPMJMS2067), "Scalable and Robust Integrated Quantum Communication System" (Project Manager (PM): Shota Nagayama, Project Associate Professor, Graduate School of Media and Governance, Keio University) (JPMJMS226C), JST Strategic Basic Research Programs, individual-type research (PRESTO), "Creation of Innovative Quantum Information Processing Technology Infrastructure" (Research Supervisor: Akihisa Tomita) research subject "Quantum computer system architecture study for reliability" (JPMJPR2015), JST Strategic Basic Research Program, team-type research (CREST), "Exploring Quantum Frontiers Through Quantum-Classical Interdisciplinary Fusion" (Research supervisor: Nobuyuki Imoto), Co-creative multi-layer design of distributed quantum computing and its implementation (JPMJCR23I4), "Exploring the Utilization of Fault-Tolerant Quantum Computers by Using Classical Computers Cooperatively" (JPMJCR24I4), JST Open Innovation Platforms for Industry-academia Co-creation (COI-NEXT) "Center of Innovation for Sustainable Quantum AI" (JPMJPF2221), JST Support for Pioneering Research Initiated by Next Generation (SPRING) "Fostering Advanced Human Resources to Lead Green Transformation (GX)" (JPMJSP2108), Ministry of Education, Culture, Sports, Science and Technology, Quantum Leap Flagship Program (MEXT Q-LEAP) (JPMXS0120319794, JPMXS0118068682), and Grant-in-Aid for Scientific Research (22 H05000, 22 K17868, 24 K02915).

"One of the contributions from theoretical research toward the realization of large-scale fault-tolerant quantum computers is the development of an architecture of a quantum computer that excels in both versatility and extensibility, building upon fundamental research. In this research, the structure of quantum computers was reexamined based on the mechanism of modern conventional computers and the unique characteristics and properties of quantum mechanics. By redefining the functions of the memory and processor of quantum computers, the research team has proposed an architecture that significantly enhances performance and scalability. This achievement is the key to bridging the gap between theory and implementation in the rapidly advancing field of quantum computation. It is also the result of a collaborative effort by researchers with diverse backgrounds—a strength unique to this project." - Masato Koashi, Project Manager

"Surface codes are currently the most advanced error-correcting method for realizing fault-tolerant quantum computers. However, this method requires a very large number of physical qubits, posing a major challenge in realizing quantum acceleration at a practical scale. This study addresses this challenge by proposing a load-store architecture for quantum computers, leveraging both the theoretical properties of surface codes and knowledge of computer design. By applying this approach, we successfully reduced the required number of physical qubits by half while maintaining quantum computation performance. This achievement is a result of interdisciplinary collaboration within Moonshot projects and represents a significant step toward the realization of large-scale, fault-tolerant quantum computing." - Tsuyoshi Yamamoto, Project Manager

"Reducing the hardware resource requirement is crucial for early realization of fault-tolerant quantum computers. This study proposes a quantum computer architecture that applies the surface code properties from a computer design perspective, reducing the number of qubits by 50% without significantly increasing execution time. Notably, this method does not alter the fundamental specifications of surface codes or hardware, making it a highly impactful advancement. It challenges previous assumptions in quantum resource estimation for practical implementation and has far-reaching implications. This Achievement is a testament to the strength of Moonshot research, which brings together experts from diverse fields. I look forward to further discussions and development." - Shota Nagayama, Project Manager

[Glossary]

1Fault-tolerant quantum computation

Quantum computation that corrects errors caused by noise in qubits, ensuring reliable calculations. This technology is essential for practical quantum computing.

2Computer architecture

The fundamental design of a computer, defining its components and how they interact to perform computations.

3Quantum error correcting code

A method for detecting and correcting errors for fault-tolerant quantum computing. It works by redundantly encoding logical qubits using multiple physical qubits, allowing errors in physical qubits to be identified and corrected.

4No-cloning theorem

A fundamental principle in quantum mechanics states it is impossible to create an exact copy of an arbitrary quantum state using quantum operations.

5Memory bandwidth

A measure of the amount of data that can be transferred between a processor and memory within a given period.

6Locality (of memory access)

A characteristic of data access patterns in program execution where certain data is more likely to be accessed based on its prior usage. Locality is Categorized into:

- Temporal locality: Data that has been accessed recently is likely to be accessed soon.

- Spatial locality: Data stored near a recently accessed address is likely to be accessed next.

Because most programs exhibit locality, cache structures can be optimized to enhance data access speed and overall system performance.

About NTT

NTT contributes to a sustainable society through the power of innovation. We are a leading global technology company providing services to consumers and businesses as a mobile operator, infrastructure, networks, applications, and consulting provider. Our offerings include digital business consulting, managed application services, workplace and cloud solutions, data center and edge computing, all supported by our deep global industry expertise. We are over $93B in revenue and 330,000 employees, with $3.6B in annual R&D investments. Our operations span across 80+ countries and regions, allowing us to serve clients in over 190 of them. We serve over 75% of Fortune Global 100 companies, thousands of other enterprise and government clients and millions of consumers.

Media contacts

NTT Service Innovation Laboratory Group

Public Relations

Inquiry form

Information is current as of the date of issue of the individual press release.

Please be advised that information may be outdated after that point.

NTT STORY

WEB media that thinks about the future with NTT