Microsoft ends support for Internet Explorer on June 16, 2022.

We recommend using one of the browsers listed below.

- Microsoft Edge(Latest version)

- Mozilla Firefox(Latest version)

- Google Chrome(Latest version)

- Apple Safari(Latest version)

Please contact your browser provider for download and installation instructions.

April 1, 2022

Keio University

Nippon Telegraph and Telephone Corporation

Nagoya University

RIKEN

World's First Quantum Error Correction Method Developed for Cryogenic Environments Enabling Operations between Logic Qubits

-A Major Step Toward the Realization of Large-Scale Quantum Computers-

Keio University (Minato-ku, Tokyo; President: Kohei Itoh), Nippon Telegraph and Telephone

Corporation (Chiyoda-ku, Tokyo; President: Jun Sawada), Nagoya University (Nagoya, Aichi; President: Naoshi

Sugiyama), and RIKEN (Wako, Saitama; President: Makoto Gonokami) have developed the world's first quantum error

correction algorithm that can decode multiple interacting logical qubits in a cryogenic environment with power

consumption, implementation scale, throughput, and error-correction performance meeting the requirement of the

existing technologies. Our results improve the scalability of superconducting quantum computers and fault-tolerance

of superconducting qubits, which contribute to the development of fault-tolerant quantum computers.

The team's results were published at the 28th IEEE International Symposium on High-Performance Computer

Architecture (HPCA-28) to be held from April 2, 2022.

1. Points

- The team proposed a novel quantum error correction algorithm that enables error decoding and fault-tolerant logical operations on interacting multiple logical qubits.

- They implemented a decoding unit based on the proposed algorithm with single-flux-quantum circuits. Due to their high operating frequency and low power consumption, their quantum error correction scheme can protect multiple logical qubits under logical operations from errors within the restricted power consumption in cryogenic environments.

- This technology is expected to contribute to the development of fault-tolerant quantum computers.

2. Background

Quantum computers are a technology that can perform calculations by making use of quantum mechanics

phenomena such as superposition and entanglement. Quantum computers are actively developed in the world due to their

ability to solve vital problems in cryptography and quantum chemistry faster than previously existing computers.

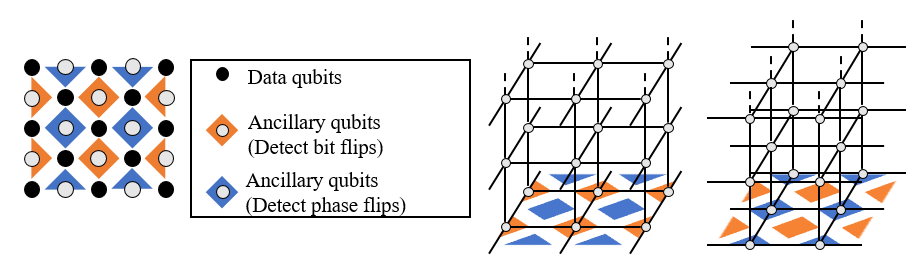

Since the elements of the quantum computers, qubits, have high error rates, the framework of quantum error correction

has been investigated to correct errors during the computation by constructing a logical qubit with several noisy

physical qubits, as shown on the left side of Figure 1.

Figure 1. Left: Surface code; Right: Three dimensional

lattices by stacking measurement values of surface codes

Figure 1. Left: Surface code; Right: Three dimensional

lattices by stacking measurement values of surface codes

Surface codes, which are one of the most popular quantum error-correcting codes, consists of data

qubits and ancillary qubits (left side of Figure 1). Values called syndromes are obtained from the ancillary qubits in

each cycle of computation, and the decoding process of surface codes is attributed to the graph matching problem on

syndrome values. Classical computers that solve the graph matching problems to estimate the errors in quantum devices

are called decoding units. High-performance decoding units are required to construct fault-tolerant quantum computers.

In practice, errors may also occur in the measurements of ancillary qubits. Even such cases, one can reliably estimate

errors by solving a graph matching problem on a three-dimensional lattice constructed by stacking the obtained

syndrome values in several cycles in the time direction (right side of Figure 1).

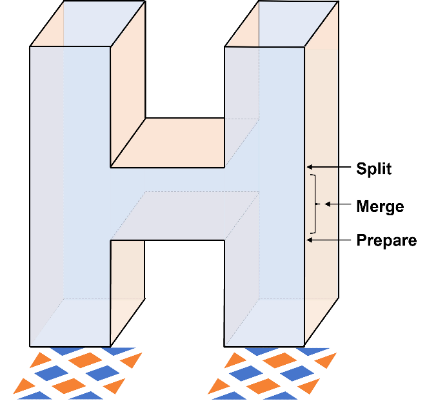

To perform quantum computation using logical qubits protected by surface codes, it is necessary to perform logical

operations in a fault-tolerant manner. Lattice surgery enables fault-tolerant operations between logical qubits by

merging and splitting the codes of multiple logical qubits encoded with surface codes, and this operation is known to

be one of the essential operations in realizing arbitrary quantum operations. The decoding process during the lattice

surgery corresponds to solving a complicated graph matching problem in which the boundary of logical qubits

dynamically changes due to the merge and split of logical qubits (Figure 2). However, the existing decoding methods

can only decode independent single logical qubits and cannot perform error correction of logical qubits during lattice

surgery.

Figure 2. The shape of a lattice of graph matching problem

during a lattice-surgery operation

Figure 2. The shape of a lattice of graph matching problem

during a lattice-surgery operation

3. Results

In this research, the team proposed a decoding algorithm compatible with lattice surgery. This was based on a decoding scheme previously proposed by the same group called "online decoding," which follows the occurrence of errors in qubits and prevents the accumulation of errors by estimating errors in real-time.1 This is expected to enable fast correction of errors on logical qubits during quantum operations.

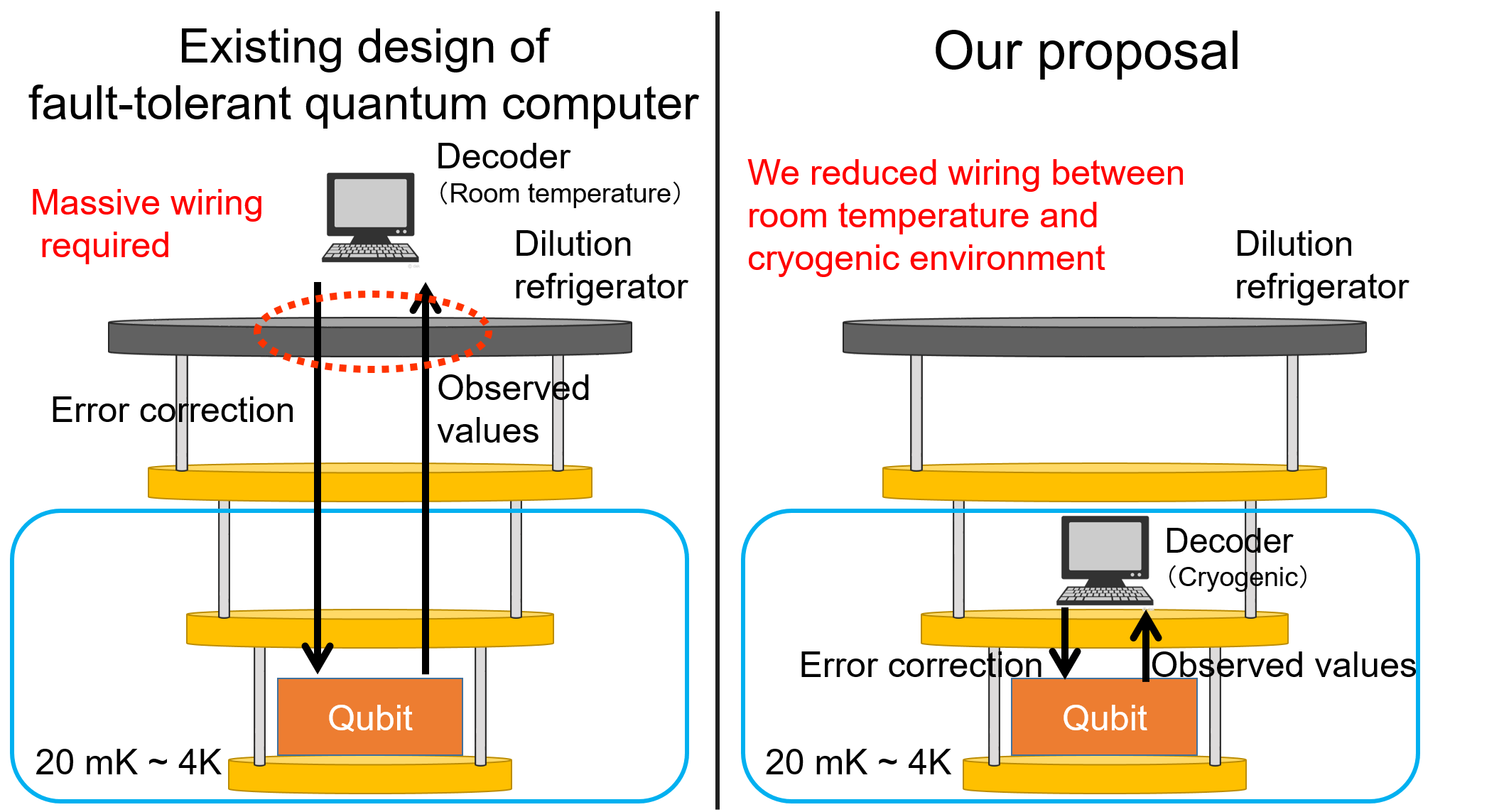

Superconducting qubits are promising candidates as quantum computer devices due to their scalability. Since they can only be operated in cryogenic environments, they are usually installed in dilution refrigerators. Meanwhile, it is supposed that decoders operate at room temperature because conventional CMOS-based implementations consume too much energy in cryogenic environments. Therefore, the large amount of wiring between a room and cryogenic temperatures limits the scalability of superconducting quantum computers (left side of Figure 3).

This team has designed a decoder based on the proposed algorithm that can be operated in a cryogenic environment using single-flux-quantum (SFQ) circuits. The SFQ circuits are superconductor circuits that can be operated at a high frequency with low power consumption. This can dramatically improve the scalability of quantum computers (right side of Figure 3). Furthermore, their decoder can finish the decoding process in less than 1 microsecond per cycle, which is fast enough to prevent accumulation of errors. These improvements are expected to contribute to the development of fault-tolerant quantum computers with superconducting qubits.2

Figure 3.Structures of superconducting fault-tolerant

quantum computing (Left: existing approach, Right: Our proposal)

Figure 3.Structures of superconducting fault-tolerant

quantum computing (Left: existing approach, Right: Our proposal)

4. Perspective

This team has proposed a fast error-correction method for multiple logical qubits with performing logical operations in a cryogenic environment, thereby improving the scalability of superconducting quantum computers and the fault-tolerance of qubits. These results are expected to contribute to the development of fault-tolerant quantum computers.

<Funding>

This work is supported by JST Mirai Program (Grant No. JPMJMI18E1); CREST, JST (Grant No. JPMJCR18K1); PRESTO, JST (Grant No. JPMJPR1916); ERATO, JST (Grant No. JPMJER1601); MEXT Q-LEAP (Grant No. JPMXS0120319794, JPMXS0118068682); Moonshot R&D, JST (Grant No. JPMJMS2061); the ANRI Fellowship.

<References>

1.Yosuke Ueno, Masaaki Kondo, Masamitsu Tanaka, Yasunari Suzuki, Yutaka Tabuchi, "QECOOL: On-Line Quantum Error Correction with a Superconducting Decoder for Surface Code", The 58th Design Automation Conference(DAC'21), 2021.

2.Press release "Development of Quantum Error

Correction Method for Superconducting Quantum Computers in Cryogenic Environments - World's First Realization of a

Key Technology for the Development of Large-Scale Quantum Computers -"(November 8 , 2021)

https://group.ntt/jp/newsrelease/2021/11/08/211108b.html

<Paper information>

Yosuke Ueno, Masaaki Kondo, Masamitsu Tanaka, Yasunari Suzuki, Yutaka Tabuchi, "QULATIS: A Quantum

Error Correction Methodology toward Lattice Surgery", the 28th IEEE International Symposium on High-Performance

Computer Architecture (HPCA), 2022.

doi: 10.1109/HPCA53966.2022.00028

*Please direct any requests or inquires to the contact information provided below.

Inquiries about research

Department of Information and Computer Science,

Faculty of Science and Technology, Keio University

Professor Masaaki Kondo

Tel: +81-45-566-1599 Fax: +81-45-566- 1599 E-mail: kondo@acsl.ics.keio.ac.jp

https://www.acsl.ics.keio.ac.jp/

Inquiries about press release

Keio University

Tel: +81-3-5427-1541 Fax: +81-3-5441-7640 Email: m-pr@adst.keio.ac.jp

https://www.keio.ac.jp/en/

Nippon Telegraph and Telephone Corporation

Email: nttrd-pr@ml.ntt.com

Nagoya University

Email: kouho-en@adm.nagoya-u.ac.jp https://en.nagoya-u.ac.jp/

RIKEN

Email: ex-press@riken.jp

Information is current as of the date of issue of the individual press release.

Please be advised that information may be outdated after that point.

NTT STORY

WEB media that thinks about the future with NTT